在電子應用中,使用兩個PMOS管背靠背連接是常見的電路設計,其主要目的是為了提高電路的穩定性和可靠性。

那麼,兩個PMOS管背靠背連接,是串聯還是並聯?事實上,兩者都是,即存在串聯和並聯兩種方式。今天我們主要帶著以下二個核心展開講解:

1. 串聯與並聯的電路設計的目的

2. 為什麼不能只用一個PMOS?

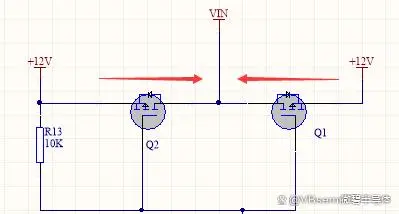

2個PMOS並聯,如圖

可以看到,當Q1和Q2(PMOS)導通時,左右兩邊+12V並聯增加電流,目的是為了提高VIN(輸出端)的帶載能力,用來給模組供電。

在這裏的兩個PMOS管用處就很清楚了:起到分流的作用,因為VIN負載電流會比較大。

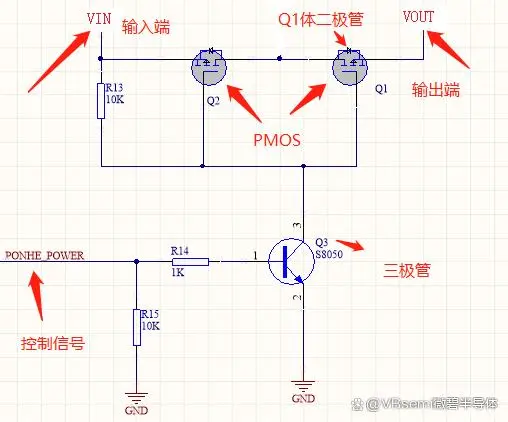

在這裏對電路設計解釋:

控制信號,也就是PHONE_POWER;

當它輸出高電平時,三極管Q3導通,兩個PMOS Q1和Q2導通,VIN輸出端會等於+12V;當它輸出低電平時,三極管Q3截止,兩個PMOS Q1和Q2截止,VIN輸出端會等於0V;

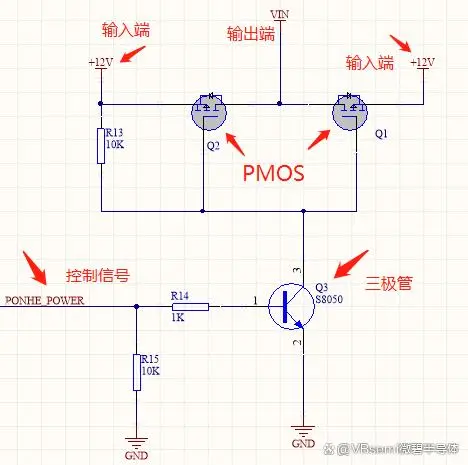

2個PMOS串聯,如圖

可以看到兩個MOS管串聯,對電路設計解釋:

控制信號,也就是PHONE_POWER;

當它輸出高電平時,三極管Q3導通,兩個PMOS Q1和Q2導通,VIN輸入端會等於VOUT輸出端;

當它輸出低電平時,三極管Q3截止,兩個PMOS Q1和Q2截止,VIN輸出端會等於0V;

當需要外接輸出端VOUT進行調試時,兩個PMOS管進行關閉,可以防止輸出端VOUT的電流串到VIN輸入端處;如果沒有Q1,即輸出端VOUT電流從Q2的體二極體串到VIN輸入端處。

原理是體二極體的反向截止特性:Q1(左正右負),Q2(左負右正)

那麼,為什麼不能只用一個MOS管呢?

現在我們來討論下電路設計:

假設VIN負載最大電流為1A,電路中並聯使用兩個PMOS,每個PMOS管的IDS電流就會在0.5A以上。

那麼問題來了,我們能保證兩個管子都是0.5A嗎?如果一個是0.7A,一個是0.3A或者一個0.6A,一個0.4A,那其中一個管子不就 因為電流過大而發熱甚至導致燒毀?

首先會想到的是,使用兩個RDS(on)同樣的MOS管,這樣流經的電流就會一致了。

但 俗話說得好,這個世界上沒有兩片完全相同的樹葉。MOS管也一樣,兩個管子同樣會存在製造工藝的差異以及其他參數的不一致。

這時候有沒有朋友想到我們發過的一期文章?就是MOS管的均流設計。

還是和MOS管的RDS(on)有關,小編看到有朋友是這麼說的。

MOS管的RDS(on)和溫度是呈正係數關係,即隨著溫度的升高,RDS(on)會增大。

由於Q1流過的電流會比Q2大,所以Q1的溫升肯定比Q2高,這時候Q1的RDS(on)會增大,RDS(on)增大後,流過Q1的電流又會變小,形成一個完整的負回饋,並實現了均流。

不過,想要更保險起見的話,建議選擇MOS管時保有餘量。比如VIN的最大負載是1A,那麼兩個PMOS管就可以選擇0.6~0.7A的IDS。並且最好選擇一致的型號。

這種電路設計的優點,微碧給大家簡單進行了以下整理:

1. 電流共用,避免電流過大損壞器件的風險;

2. 增加開關速度,兩個並聯能夠減小整個電路的開關時間,電阻越小,開關速度越快;

3. 降低電磁干擾,背靠背連接能夠減小開關過程中產生的電磁干擾;

4. 提高電路的可靠性,當一個PMOS管出現故障時,另一個PMOS管仍然可以繼續工作;

5. 降低成本,選擇MOS管時可以在一定程度上降低總成本。

相關的優勢與應用分析後面我們有機會再進行探討!

看到這裏的你是否可以點個贊或者關注一下呢!十分感謝您的支持!有什麼疑問或者想要探討的話題可以在評論區一起交流學習噢!

以上部分圖片和資料來源於網路

* 如果您需要申請我司樣品,請填寫表格提交,我們會24小時內回復您